ICCK Transactions on Circuits and Systems | Volume 1, Issue 1: 1-10, 2025 | DOI: 10.62762/TCAS.2025.881344

Abstract

With the increasing complexity of neural network models, the Network-on-Chip (NoC) has become a critical communication backbone in heterogeneous computing architectures. However, existing NoC simulation tools often fall short in supporting diverse computational units such as matrix processors and RISC-V programmable cores, limiting their ability to meet the stringent demands of real-time performance, high throughput, and energy efficiency in large-scale AI workloads. To overcome these limitations, this paper presents a behavior-level NoC simulation framework tailored for heterogeneous computing environments. The framework features precise node-level modeling, a dynamic pipelining mechanism,... More >

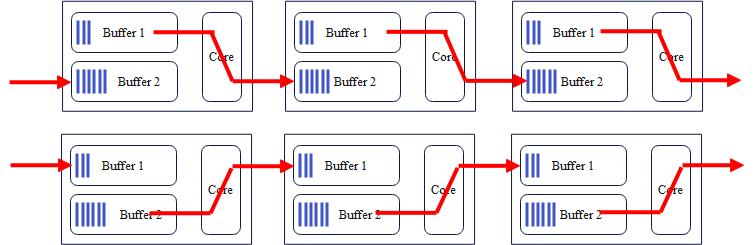

Graphical Abstract